利用FPGA优化工业以太网交换机设计

在工业自动化与智能制造高速发展的今天,工业以太网作为骨干通信网络,其性能直接关系到整个系统的实时性、可靠性与稳定性。传统的基于专用交换芯片的工业以太网交换机设计,虽然在通用性上表现良好,但在应对特定工业场景的严苛要求(如极低延迟、高精度时钟同步、确定性的流量调度)时,往往存在灵活性不足、优化空间有限的瓶颈。现场可编程门阵列(FPGA)以其并行处理、硬件可重构和低延迟的独特优势,为工业以太网交换机的深度优化设计提供了极具潜力的解决方案。

一、传统设计挑战与FPGA的引入

传统工业以太网交换机核心依赖于商用交换芯片(ASIC)。这类芯片功能固化,虽然支持标准协议(如IEEE 802.1Q VLAN, IEEE 1588 PTP),但其数据转发流水线、队列管理机制和调度算法是固定的。在面临以下需求时显得力不从心:

- 超低且确定的延迟:对于运动控制、机器人协同等应用,网络抖动需控制在微秒甚至纳秒级。

- 定制化协议处理:许多工业现场总线协议(如PROFINET IRT, EtherCAT)或行业专用协议需要深度集成和特殊帧处理,通用芯片难以高效支持。

- 灵活的网络拓扑与流量工程:需要根据实时工况动态调整优先级策略、带宽预留或实现环形冗余协议的快速自愈(如MRP, HSR/PRP)。

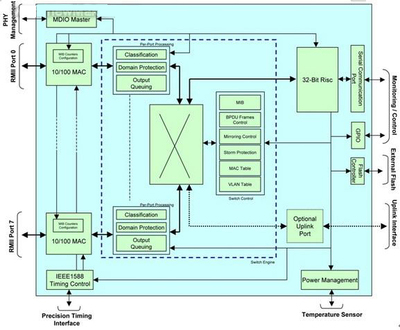

FPGA的引入,使得交换机的核心数据平面可以从“固定流水线”转变为“可编程硬件”。设计者可以将关键的、对性能敏感的网络功能(如帧解析、分类、队列管理、时间戳插入/提取、调度器)以硬件逻辑的形式在FPGA中实现,从而获得接近线速的处理能力和极致的确定性。

二、FPGA优化设计的关键领域

利用FPGA优化工业以太网交换机设计,主要围绕以下几个核心领域展开:

- 确定性的数据通路设计:

- 并行处理架构:在FPGA内设计多路并行输入/输出引擎和查找引擎,打破传统串行处理瓶颈,实现多端口同时、无阻塞的帧转发。

- 精细化流量控制:设计基于信用的整形器(Shaper)和优先级队列(通常可支持8个以上优先级),并可在硬件层面实现复杂的调度算法,如严格优先级(SP)、加权公平队列(WFQ)甚至时间感知整形器(TAS,IEEE 802.1Qbv),为时间敏感网络(TSN)打下基础。

- 极低延迟交换:通过优化流水线设计,减少存储转发(Store-and-Forward)带来的延迟,甚至实现直通(Cut-Through)交换,将端口到端口的转发延迟降至数百纳秒。

- 高精度时间同步增强:

- 工业通信对时钟同步要求极高。FPGA可以集成高精度的IEEE 1588(PTP)硬件时钟从端或主端。利用FPGA内部的锁相环(PLL)和硬核计数器,在物理层精确打时间戳,规避了软件栈处理带来的不确定性和抖动,可将同步精度提升至亚微秒级别。

- 定制化协议卸载与加速:

- 对于EtherCAT等需要在帧传输过程中实时处理和修改数据的协议,FPGA可以将其数据链路层处理逻辑完全硬件化,实现“在飞”处理,极大减轻主CPU负担并提升响应速度。

- 可以集成用户自定义的帧头解析、过滤和动作逻辑,灵活支持非标或私有工业协议。

- 增强的可靠性与安全性:

- 硬件级冗余:在FPGA内实现冗余协议(如HSR/PRP)的帧复制、标签插入和重复帧丢弃逻辑,实现无缝零延时切换。

- 硬件安全引擎:集成流分类和访问控制列表(ACL)硬核,对非法流量进行线速过滤;甚至可实现MACsec等加密协议的硬件加解密,保障数据安全而不影响转发性能。

三、系统设计与工程实践

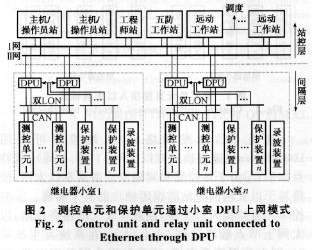

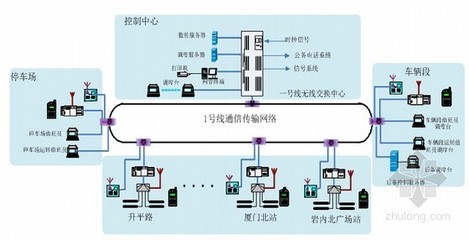

一个典型的基于FPGA的工业以太网交换机系统架构通常包括:

- FPGA核心交换矩阵:实现上述所有数据平面的优化功能。

- 高速SerDes接口:连接外部PHY芯片,支持千兆/万兆以太网。

- 嵌入式处理器系统:可以是FPGA内部的软核(如NIOS II、MicroBlaze)或外置的MPU,用于运行网络管理协议栈(如SNMP、Web服务器)、配置FPGA逻辑以及处理少量的控制平面报文。

- 外部存储器:DDR用于存储转发表、统计信息及缓冲数据包。

设计流程上,需采用硬件描述语言(如VHDL/Verilog)进行RTL设计,并利用厂商提供的IP核(如以太网MAC、DDR控制器、PTP时钟)加速开发。必须进行严格的时序约束、仿真验证以及在实际网络环境下的性能测试(如RFC 2544)。

四、优势与挑战

优势:

性能极致:实现超低延迟、高吞吐量和确定性的转发。

灵活可重构:可通过更新比特流文件适应新的协议或需求,延长产品生命周期。

* 高度集成:将交换、处理、同步等功能集成于单芯片,降低系统复杂度与功耗。

挑战:

开发门槛高:需要专业的FPGA设计知识和网络协议深度理解,开发周期较长。

成本考量:高端FPGA芯片成本高于通用交换芯片,适合对性能有极端要求或需要差异化的高端应用。

* 功耗与散热:复杂设计可能带来更高的功耗,需要仔细的功耗分析和散热设计。

###

利用FPGA实现工业以太网交换机的设计优化,代表了工业网络设备向高性能、定制化和确定性方向演进的重要趋势。它并非要完全取代传统ASIC方案,而是在那些对网络性能有严苛要求的尖端工业场景中,提供了无可替代的解决方案。随着FPGA开发工具的成熟、IP生态的丰富以及TSN等标准技术的普及,基于FPGA的工业以太网交换机将在高端制造、能源电力、轨道交通等领域发挥越来越关键的作用,为构建真正可靠的工业互联网基础设施提供核心动力。

如若转载,请注明出处:http://www.ccloud-tech.com/product/74.html

更新时间:2026-04-30 21:27:20